在D類功放IC設計應用中需注意以下幾點:

1 Deadtime(死區校正)

全橋MOSFET管輪流成對導通,理想狀态一對導通,另一對截止,但實際上功率管的開啓關斷有一個過程。過渡過程中,必有一瞬間,如圖3所示,在IN1/IN3尚未徹(chè)底關斷時IN2/IN4就已開始導通;因MOSFET全部跨接於(yú)電源兩端,故極端的時間内,可能會有很大的電壓電流同時加在4個MOSFET上,導緻功耗很大,整體效率下降,而且器件溫升加劇,燒壞MOSFET,降低可靠性。爲避免兩對MOSFET同處導通狀态,引起有潛在威脅的很大短路電流,應保證一對MOSFET導通和另一對MOSFET截止期間有一個很短的停滞死區時間(Dead-time),這個時間由Logic邏輯控制器控制,以有效保證一組MOSFET關斷後,另一組MOSFET再适時開啓,減小MOSFET損耗,提高放大器效率。

但Deadtime設(shè)置不當(dāng),将出現如下問題:

(1)輸出信号中将産(chǎn)生毛刺,造成電磁幹擾,也即死區時間内,IN1/IN3都關斷。完全失控的輸出電壓将受到圖6(a)中體二極管電流的影響(體二極管電流的形成,參(cān)見下文EMI節),輸出波形中将出現毛刺幹擾。

(2)Deadtime過(guò)大,輸出波形中出現的毛刺包含的能量将持續消耗在體二極(jí)管中,以熱能形式消耗能量,嚴重影響芯片工作穩定性和輸出效率。

(3)Deadtime過(guò)長(zhǎng),影響放大器線性度,造成輸出信号交越失真,時間越長(zhǎng),失真越嚴重。

2 EMI(Electro-Magnetic InteRFerence)

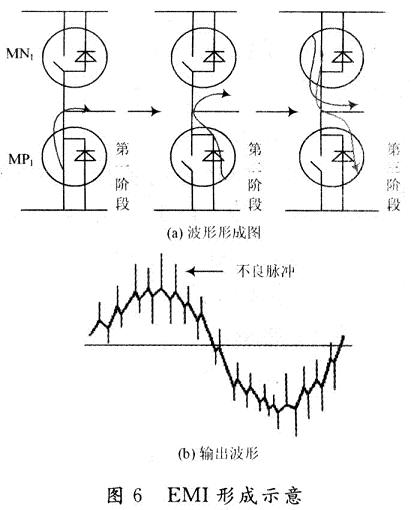

EMI主要由MOSFET體二極管反向恢複電(diàn)荷形成,具體産(chǎn)生機理如圖6所示。

第一階段,MP1-MOSFET導通,有電流流過MOSFET和後級LPF電感;第二階段,全橋進入Dead-time期間,MP1本身關斷,但其體二極管依然導通,保證後級電感繼續續流;第三階段,Deadtime期結束,MN1導通瞬間,若MP1體二極管存儲的剩餘電荷尚未完全釋放,則瞬間釋放上一次導通期間未釋放的存儲電荷,導緻反向恢複電流激增,此電流趨向於(yú)形成一個尖脈沖(chōng),最終體現在輸出波形上,如圖6(b)所示。因此,輸出頻譜會在開關頻率以及開關頻率倍頻處包含大量頻譜能量,對外形成EMI。

爲抑制EMI,以降低輸出方波頻率,減緩方波頂部脈沖爲目的,将一些内部EMI消除電路新技術應用於(yú)新産(chǎn)品中:

(1)Dither。擴展頻譜技術,即在規定範圍内,周期性調(diào)整三角波採(cǎi)樣時鍾頻率,基波和高次諧波避開敏感頻段,使輸出頻譜能量平坦分散;

(2)增加主動輻射限制電(diàn)路,輸出瞬變(biàn)時,主動控制輸出MOSFET栅極,以避免後級感性負載續流引起高頻輻射。

3 印制闆PCB布局設計規則

(1)因輸出信号含大量高頻方波,需将加入的低失真、低插入損耗LC濾波電(diàn)容和鐵氧體電(diàn)感低通濾波器件緊密靠近功放,将承載高頻電(diàn)流的環路面積減至最小,以降低瞬态EMI輻(fú)射。

(2)因輸出電(diàn)流大,音頻輸出線徑要寬,線長(zhǎng)要減短,故需降低無源電(diàn)阻RP和濾波器電(diàn)阻RF,提高負載電(diàn)阻RL比值,提高輸出效率。

(3)PCB底部是熱阻最低的散熱通道,功放底部裸露散熱銅皮面積要大,應盡可能在敷銅塊與臨近具有等電(diàn)勢的引腳以及其他元件間多覆銅,裸露焊盤相接的敷銅塊用多個過孔連接到PCB闆背面其他敷銅塊上,該(gāi)敷銅塊在滿足系統信号走線要求下,應具有盡可能大的面積,以保證芯片内核通過這些熱阻最低的敷銅區域有最佳散熱特性。

(4)大電流器件接地端附近,多加過孔,信号若跨接於(yú)PCB兩層(céng)間,多加過孔提高連接可靠性,降低導通阻抗。

(5)信号輸入端元件焊盤和信号線與輸出端保持适當(dāng)間距,關(guān)鍵反饋網絡器件置放在輸入/輸出PCB布局模塊中間,防止輸出端EMI幅射影響輸入端小信号。

(6)地線、電源線遠離輸入/輸出級,採(cǎi)用單(dān)點接地方法。 |